## HARMONIC FILTER IN ITS EXPERIMENTAL ENVIRONMENT

N. Obeidi, B. Belmadani and E. Bounadja

Electric engineering and renewable energy laboratory (LGEER), University of chlef, Algeria.

Received: 11 March 2020 / Revised: 30 April 2020 / Accepted: 15 May 2020 /

Abstract—the strategies rely in particular on the implementation, at the level of the insulation of current harmonics, of a highly selective filter, called "multi-variable filter". The experimental validation of different active filter control strategies parallel to these two structures and their controls are intended to compensate harmonic currents of the nonlinear loads connected to networks and to improve the performance of the filtering while resorting to control strategies of reduced complexity. These works were validated by simulation using MATLAB / Simulink tools.

*Keywords*—Active Filter, Current Harmonic, Reel-Time Interface (RTI), Nonlinear Load, Pulse Width Modulation (PWM).

### 1. Introduction

The electrical networks face a non-good phenomenon called electrical harmonic generated due to non-linear loads. This phenomenon distorts the electrical current of the source, which leads to losses in electrical energy [1].

This paper is devoted to the practical realization of an experimental test bench for active three-phase parallel filtering. Then, the experimental results will be presented to validate the concepts and commands already mentioned before. The power scheme requires the use of the three-phase electrical network to power two static converter bridges[2]; the first bridge being diodes (three-phase diode rectifier bridge), behaving as a non-linear load for the electrical network, while the second bridge being a thyristor voltage inverter with two voltage levels. The voltage inverter is connected to the parallel network through 3 inductors for smoothing and filtering the measured harmonic currents. On the load side, the diode bridge supplies an RL load.

The active filter control can be broken down into two parts:

- Extraction of reference harmonic currents by the multi-variable filter (FMV) technique[3].

- The continuation of these reference currents according to two hysteresis and PWM modulation techniques[4].

To do this, a first test is performed to first generate the three reference currents numerically from the dSPACE1104 control unit of our LGEER laboratory. The pursuit of these harmonic current references requires a real-time comparison with the actual currents measured by current sensors in the power circuit of the active filter. The modulation technique, either in hysteresis (current control) or PWM (voltage control), is used to generate the control signals at the switches of the inverter switches. Note that the implementation of these commands on the DS1104 card, therefore, requires a sampling period of the order of 10-4s (DS1104 processor limited to this value). During this test, the DC bus of the inverter is made by a DC continuous of voltage to overcome any problem of voltage regulation[5].

Once we have ensured that the measured currents of their reference currents generated by the dSPACE control unit are perfectly tracked, we proceed to the second test identical to the previous one, except that we now have to generate the three current harmonic references (references from the active filter) in the three star-coupled inductances. This test requires the implementation of the pollutant load, the network, the 5V / 15V adapter card, and the dSPACE system. The dSPACE system then establishes current harmonic references using the instantaneous powers method[6].

Finally, the third test implements the complete system that takes the previously validated elements and then requires the regulation of the voltage across the continuous bus filter.

Corresponding author: E-mail: bounadja@univ-chlef.dz

Copyright © J. Sc. & Tech, 2020 Vol 02, Issue 01 -14, pp 83-90

# 2. Materials and methods global schema of power

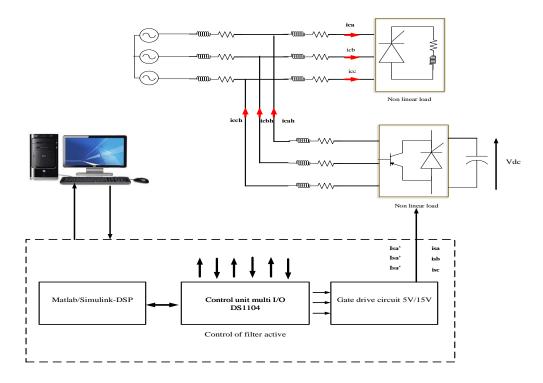

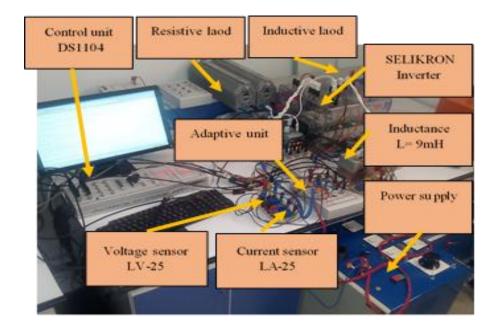

The experimental platform produced is given by Figure 1 and is composed of the following elements:

- The polluting load (Rectifier Bridge with diodes + load RL);

- Parallel active filter (2-level voltage inverter, filter inductors and capacitors);

- Active filter control (dSPACE system, analog card, and triangular signal generator).

Figure 1. General topology of editing under study.

# 2.1. The Parallel Active Filter

The parallel active filter is composed of a two-level voltage inverter powered by two series-biased capacitors (non-reversible in voltage) of  $2200\mu F$  each (a capacitor of  $1100~\mu F$  equivalent). This inverter is connected to the network utilizing a three-phase inductive filter each having a value of  $L_f = 9.01mH$ . The switches of the inverter are formed by IGBTs (Insulated Gate Bipolar Transistor) transistors. These are components manufactured by SEMIKRON, specifically SKM50GB123D 1200V / 50A modules including diodes placed in anti-parallel IGBTs. The opening and closing of the IGBTs are controlled by the SEMIKRON brand SKHI 22A (control voltage 0 / 15V) drivers. These drivers include power component protection and dead time management elements.

### 2.2. Active Filter Control

The principle of the active filter control is given in Figure 2. The active filter control generates the switching commands of the inverter voltage switches and includes three main functions [7]:

- Identification of harmonic currents of the non linear load,

- Regulation of voltage  $V_{dc}$ ,

- Continuation of current harmonic references.

### 2.3. Technique of control

In this study, we control the two interrupters of the same arm in a complementary technique: the conduction of one leads to the blocking of the other. based on this technique, the opening and closing of the inverter switches depend on the state of three control signals (Y1, Y2, Y3), defined below:

$$Y1\begin{cases} 1 & \text{SO} & S1 \\ 0 & S2 \end{cases}$$

S1 close and S4 open S4 close and S1 open S2

$$Y2\begin{cases} 1 & \text{SO} & S2 \\ 0 & S5 \end{cases}$$

S2 close and S5 open S5 close and S2 open S3 close and S6 open S6 close and S3 open S6 close and S3 open

In practice, the two interrupters of the same arm must never drive at the same time to avoid short-circuit, it is, therefore, necessary to generate a dead time, between the command to block a switch and the command to strike the other switch of the same arm. Thus, from the states of the switches presented by the variables Y1, Y2, and Y3, respectively, eight possible cases are obtained for the output of the active filter as shown in Table 1.Besides,  $V_{kM} = Y_k V_{dc}$  The  $k^{th}$ -phase dynamic system of the filter's model is illustrated by the following equation after a switching state function  $d_{nk}$ as:

$$d_{nk} = \left(Y_k - \frac{1}{3} \sum_{m=1}^{3} Y_m\right)_{m} \tag{1}$$

According to (1) and for the eight possible switching states of the filter, the conversion from  $[Y_k]$  to  $[d_{nk}]$  is shown in Table 1. The DC bus derived from follow equation:

$$\frac{dV_{dc}}{dt} = \frac{1}{C_{dc}} \times i_{dc} \qquad V_{dc} = \frac{3\sqrt{6} \times V_{RMS}}{\pi}$$

(2)

Table.1 Switching States of FAP.

| Vout(a)               | Vout(b)               | Vout(c)               | Y1 | Y2 | Y3 | case |

|-----------------------|-----------------------|-----------------------|----|----|----|------|

| 0                     | 0                     | 0                     | 0  | 0  | 0  | 0    |

| $2V_{dc}/3$           | - V <sub>dc</sub> /3  | - V <sub>dc</sub> /3  | 1  | 0  | 0  | 1    |

| - V <sub>dc</sub> /3  | 2 V <sub>dc</sub> /3  | -V <sub>dc</sub> /3   | 0  | 1  | 0  | 2    |

| V <sub>dc</sub> /3    | V <sub>dc</sub> /3    | -2 V <sub>dc</sub> /3 | 1  | 1  | 0  | 3    |

| -V <sub>dc</sub> /3   | -V <sub>dc</sub> /3   | 2 V <sub>dc</sub> /3  | 0  | 0  | 1  | 4    |

| V <sub>dc</sub> /3    | -2 V <sub>dc</sub> /3 | V <sub>dc</sub> /3    | 1  | 0  | 1  | 5    |

| -2 V <sub>dc</sub> /3 | V <sub>dc</sub> /3    | V <sub>dc</sub> /3    | 0  | 1  | 1  | 6    |

| 0                     | 0                     | 0                     | 1  | 1  | 1  | 7    |

## 1. Experimental results

### 4.1. References tracking test

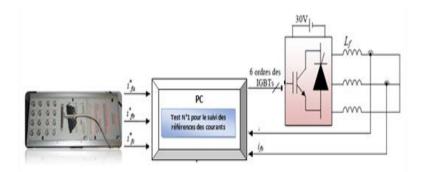

In order to ensure perfect tracking of the reference signals, the first test aims to first generate three sinusoidal reference signals (current images) numerically from the dSPACE1104 map of our LGEA laboratory. The pursuit of these current references requires a real-time comparison with the actual currents measured by current sensors in the power circuit of the active filter. The modulation technique, either in hysteresis (current control) or PWM (voltage control), is used to generate the control signals at the switches of the inverter switches. Note that the implementation of these commands on the DS1104 card therefore requires a sampling period of the order of 10-4s (DS1104 processor limited to this value). During this test, the DC bus of the inverter is made by a continuous source of voltage in order to overcome any problem of voltage regulation [3].

Figure 3. Diagram for the follow-up of the references of currents.

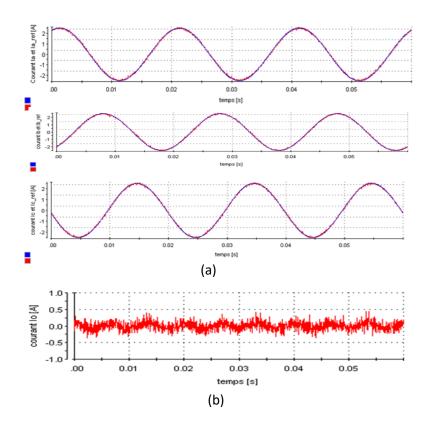

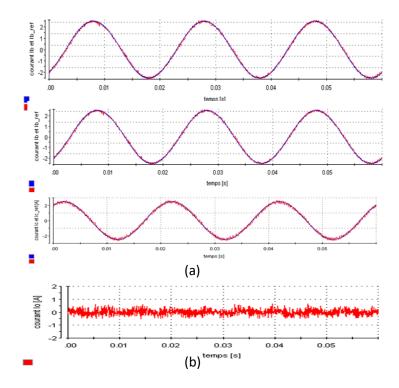

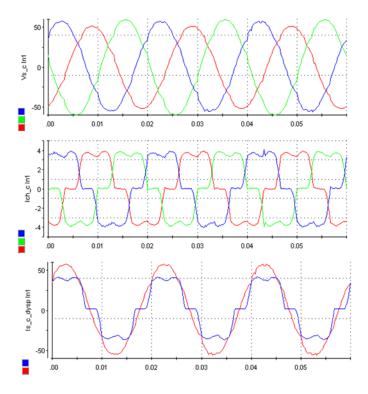

In this test, three sinusoidal current reference signals were generated from the dSPACE with amplitude of 2.5A max. These references are shifted in time by 120 °. Three current sensors placed in the load are compared to their references to generate the control signals to the inverter triggers. Note that this test is tested for two modulation techniques, namely PWM and hysteresis. The results of the test are visualized according to the figures 4 and 5. From these figures of this test, it can be concluded that the measured signals perfectly follow their references except that the hysteresis modulation has more high-frequency oscillations because of the nature of the free switching of the components (variable switching frequency) [4].

## 4.2. Full system tests

In this series of tests, the parallel active filter system and fully operational. Three sub-tests were performed, under test before the injection (the inverter is not actuated to inject the harmonic currents in opposition of phase with those of the load). A second sub-test focused on the variation of the load RL and finally a sub-test concerning the abrupt variation of the continuous bus [7].

### A. Before injection

This test is intended to show the profiles of the voltage and the current of the polluted network before the correction as well as their position one vis-à-vis the other (the phase difference between them). Note the distorted form of the network current before the correction having a very high THD harmonic distortion rate of the order of 25%.

Figure 4. (a): The three reference current references (in blue) and the three measured currents (in red) with PWM modulation technique (Lf = 9mH, carrier switching frequency fc = 15 KHz), (b): The neutral current.

Figure 5. (a): The three reference current references (in blue) and the three measured currents (in red) with Hysteresis modulation (Lf = 9mH,  $\Delta i = 0.1A$ ), (b): The neutral current.

Figure 6. Voltage and the polluted network current before injection

## B. After injection

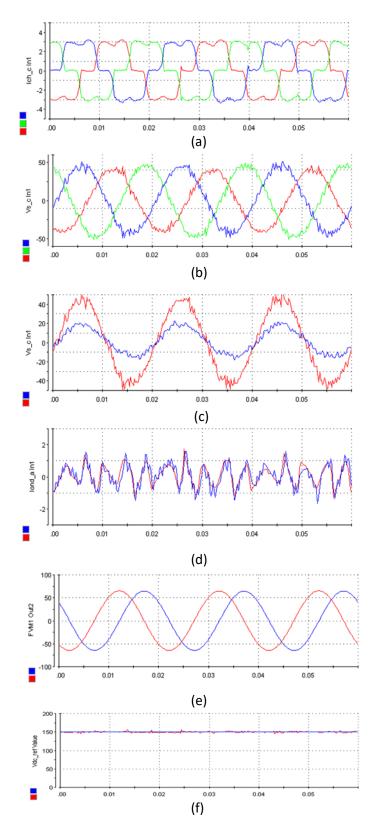

This test is intended to validate the performance of the FAP realized integrating both the performance of the FMV (the fundamentals of the voltage and the network current), the regulation of the DC bus voltage as well as the continuation of the harmonic reference currents. For this we have first presented the network voltages, the currents of the non linear load (after the connection points of the inverter with the network), the profile of the current and the voltage of the network, the harmonic currents of reference and their magnitudes measured, the fundamentals of the network voltage and current from the FMV and finally the reference and measured voltages of the DC bus. After scrolling these curves, we notice the following:

- ✓ The network current and voltage are almost sinusoidal and in phase.

- $\checkmark$  The fundamental components of the voltage (vsα, vsβ) and the current (isα, isβ) of the network are perfectly sinusoidal and offset by 90 ° in spite of the relative imbalance and the distorted form of the network voltage, which shows the effectiveness of the GMF used.

- ✓ The DC bus voltage perfectly follows its set point (150V) which shows the efficiency of the control of the DC bus (regulation used in current).

The measured harmonic currents are acceptable for their references.

Figure 7. Test results after injection:(a) Network voltages.(b) Charge currents (c) Current (Is \* 5) and phase voltage (d) Current harmonics and their references (e)Fundamental components of network voltages (vsα, vsβ), (f) DC bus voltage and reference.

*Figure 8. Overall power scheme of the test bench made at the LGEER laboratory.*

### 2. Conclusion

This article has allowed us to implement an experimental benchmark of active parallel filtering consisting of a variable voltage grid source, a 2-level voltage inverter, filter coils for smoothing currents, a non-linear load what is the diode rectifier bridge with a load RL, the current and voltage sensors, a dSpace card 1104 with adapter card 5 / 15V. The control desk module allows interfacing between measurements and set points (power / control).

A series of tests were carried out ranging from basic tests (reference tracking test + reference harmonics extraction test by two methods FMV and FPB) to the test bench of the complete active filter.

The experimental results show the concordance, from a point of view profile, between the results of simulations carried out in the third section and those obtained experimentally in the fourth section thus validating the theoretical concepts acquired on the active filtering. Indeed, these results enabled us to validate the efficiency of the current harmonic extraction method as well as current reference tracking techniques. Note the lack of time for the delivery of the experimental part because of the unavailability of the necessary equipment.

## References

- [1] M. M. Abdusalam, (2008), Structures et stratégies de commande des filtres actifs parallèle et hybride avec validations expérimentales, Ph.d. thesis, University of Henri Poincaré, Nancy-I, France.

- [2] H. Djeghloud, (2007), filtrage actif de puissance, Ph.d. thesis, University of Frères Mentouri, constantine, Algeria.

- [3] A.Bouafia, (2010), Techniques de commande prédictive et floue pour les systémes d'électronique de puissance : application aux redresseurs à MLI, Ph.d. thesis, Université of Ferhat Abbas, Setif, Algeria.

- [4] A. Chaoui, (2010), filtrage actif triphasé pour charges non linéaires, Ph.d. thesis, Université Farhat Abbas, Sétif, Algeria.

- [5] M. C. Benhabib,(2004), Contribution à l'étude des différentes topologies et commandes des filtres actifs parallèles à structure tension, Modélisation, simulation et validation expérimentale de la commande, Ph.d. thesis, University of Henri Poincaré, Nancy, France.

- [6] I. Ghadbane, (2016), Etude et réalisation d'un filtre actif parallèle en utilisant différentes stratégies de contrôle Ph.d. thesis, University of Mohamed kheider, Biskra, Algeria.

- [7] S. hong-scok, (2001), Control scheme for PWM converter and phase angle estimation algorithm under voltage unbalanced and/or sag condition, Ph.d. thesis, postech university, south korea.